Category:Diagrams of microprocessors

Jump to navigation

Jump to search

Media in category "Diagrams of microprocessors"

The following 191 files are in this category, out of 191 total.

-

6510 CPU Pinout.svg 113 × 230; 9 KB

-

6809 Internal Registers.svg 964 × 680; 3 KB

-

6809registers.png 948 × 675; 24 KB

-

68HC11 Block Diagram.jpg 750 × 670; 77 KB

-

8086 registers.png 406 × 412; 22 KB

-

80C517 arch.png 1,299 × 1,961; 81 KB

-

8X300.PNG 480 × 880; 26 KB

-

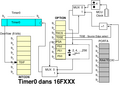

Timer0 16F84.png 515 × 368; 32 KB

-

Adresowanie segmentowe 8086.JPG 402 × 372; 17 KB

-

AMD64StateDiagram.svg 990 × 765; 23 KB

-

Architettura dell'8051.jpg 1,920 × 2,560; 351 KB

-

Architettura Itanium 2.png 1,637 × 1,412; 181 KB

-

Arkitektura e Intel 8051.png 640 × 704; 54 KB

-

Arkitektura mikro kontrollerit Intel 8051.png 674 × 540; 39 KB

-

AVX registers.svg 330 × 350; 33 KB

-

Brochage 16F84.jpg 300 × 212; 30 KB

-

CallGateDescriptor.svg 580 × 102; 4 KB

-

Capture18F.png 522 × 421; 40 KB

-

CDP1802.PNG 700 × 340; 2 KB

-

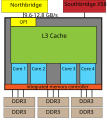

Clarkdale Arrandale Schema.png 426 × 463; 40 KB

-

Codigo de maquina.png 553 × 155; 4 KB

-

Configuratie-pini-505.png 739 × 678; 54 KB

-

Core copy.svg 534 × 600; 6 KB

-

Diag bloques 8051.JPG 700 × 707; 54 KB

-

Die 12. Generation der Intel Core-Mikroprozessoren!(极客湾Geekerwan) 03.png 3,840 × 2,160; 1,015 KB

-

DocPIC16F84 2.png 347 × 149; 7 KB

-

DocPIC16F84 3.png 449 × 123; 11 KB

-

DocPIC16F84 4.png 336 × 196; 14 KB

-

DocPIC16F84 5.png 351 × 205; 15 KB

-

DocPIC16F84 all.png 575 × 496; 56 KB

-

DocPIC16F84.png 335 × 239; 17 KB

-

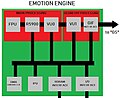

Emotion engine structure.jpg 784 × 640; 171 KB

-

Encodage des instructions de l'Intel iAPX-432.png 723 × 346; 16 KB

-

Entwicklung der Basistaktraten von Mikroprozessoren über die Zeit (DE).svg 3,519 × 1,286; 27 KB

-

Entwicklung der Basistaktraten von Mikroprozessoren über die Zeit (EN).svg 3,519 × 1,286; 27 KB

-

EsquemaHC11.gif 1,705 × 756; 67 KB

-

Flagregister.PNG 620 × 102; 3 KB

-

Flat ilm block view vlsi 600x540.jpg 600 × 540; 39 KB

-

Funktionsweise des Page Table Lookups bie Prozessoren.png 918 × 377; 18 KB

-

GateDescriptor.png 605 × 151; 4 KB

-

Generacja adresu fizycznego.JPG 490 × 491; 18 KB

-

Intel 8041 pinout.png 355 × 634; 25 KB

-

Intel 8051 arch.svg 1,273 × 1,400; 79 KB

-

Intel 8080 arch.svg 835 × 744; 65 KB

-

Intel 8080 Microprocessor.png 898 × 1,636; 145 KB

-

Intel 8080 Pinout.svg 709 × 850; 31 KB

-

Intel 8085 arch.svg 975 × 881; 90 KB

-

Intel 8086 block scheme.svg 800 × 650; 40 KB

-

Intel 8086 pinout.svg 399 × 604; 86 KB

-

Intel 8087 arch.svg 1,052 × 744; 49 KB

-

Intel 8087.svg 360 × 520; 58 KB

-

Intel 8088 segmento y offset.svg 540 × 260; 27 KB

-

Intel 8089.svg 360 × 520; 58 KB

-

Intel i8086 pinout.svg 590 × 1,052; 105 KB

-

Intel itanium arch.png 1,026 × 754; 116 KB

-

Intel MMC1 arch.svg 744 × 905; 45 KB

-

Intel MMC2 arch.svg 744 × 905; 49 KB

-

Intel Pentium arch.svg 1,116 × 807; 56 KB

-

Intel Pentium MMX arch.svg 1,215 × 807; 65 KB

-

Intel Terascale Processing Engine.svg 514 × 514; 39 KB

-

Intel Terascale Tile Arrangement.svg 443 × 383; 112 KB

-

Intel Turbo Boost Technology 2.0 20160407.jpg 600 × 313; 67 KB

-

Intel-ARL-Core-Layout.png 6,500 × 4,000; 174 KB

-

Intel486 32-bit IO Interface.png 800 × 820; 22 KB

-

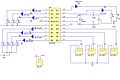

Intel486 Address decider schematic.png 1,140 × 600; 27 KB

-

Intel486 and cascading PIC.png 960 × 810; 50 KB

-

Intel486 Bus Swapping 16-bit interface.png 770 × 850; 28 KB

-

Intel486 cache.png 897 × 894; 14 KB

-

Intel486 coveyor.png 1,445 × 624; 54 KB

-

Intel486 Direct Mapped Cache.png 752 × 848; 10 KB

-

Intel486 Fully Associative Cache.png 1,030 × 710; 43 KB

-

Intel486 Logic A1 BHE BLE for 16-bit.png 900 × 810; 28 KB

-

Intel486 Logic for 74S138.png 689 × 890; 40 KB

-

Intel486 System Arbitration.png 850 × 850; 38 KB

-

Intel486 System Controller.png 806 × 895; 21 KB

-

Intel486 Translation Lookaside Buffer.png 1,210 × 770; 43 KB

-

Intel486 Two-Way Set Associative Cache.png 740 × 870; 37 KB

-

Intel486 with 82C59A.png 830 × 860; 39 KB

-

Intel486 Иерархия памяти.png 1,130 × 720; 35 KB

-

Intel486 Интерфейс 8-битных устройств.png 970 × 800; 37 KB

-

Intel486 Интерфейс устройств ВВ.png 1,150 × 800; 41 KB

-

Intel486-Typ EISA System.png 670 × 880; 47 KB

-

Intel486-Typ PCI System.png 810 × 850; 37 KB

-

Intel80860001.jpg 2,224 × 1,557; 494 KB

-

IntelProcessorRoadmap-4v.svg 1,450 × 1,350; 22 KB

-

IntelProcessorRoadmap-NoLabels.svg 512 × 91; 3 KB

-

IntelProcessorRoadmap.png 1,700 × 270; 136 KB

-

ISA Bridge schematic.png 790 × 890; 56 KB

-

Itanium arch.png 1,419 × 1,064; 63 KB

-

Itanium architecture.svg 855 × 640; 135 KB

-

Larrabee block diagram (Total pic. and CPU core bloack).PNG 900 × 810; 117 KB

-

Larrabee slide block diagram.svg 802 × 340; 32 KB

-

Larrabee.svg 539 × 486; 33 KB

-

M6800 Family Block Diagram.png 2,069 × 2,381; 194 KB

-

MC6800 Processor Diagram.png 918 × 594; 43 KB

-

MC68000-rejestry.svg 400 × 265; 45 KB

-

MC6845.svg 381 × 527; 28 KB

-

Mcs-51 pamet.png 528 × 367; 6 KB

-

Mcs-51 sfr.jpg 729 × 471; 38 KB

-

MCS-51 struktura.png 432 × 366; 2 KB

-

MCU 8051 IDE Snapshot0.png 1,024 × 723; 195 KB

-

Mechanical Revolution-Laptops mit RTX 4060 und RTX 4070 (极客湾Geekerwan) 17.png 3,840 × 2,160; 2.77 MB

-

MFrey Internal RAM MCS-51-DE.svg 600 × 450; 20 KB

-

MFrey Port 1 MCS-51.svg 475 × 500; 25 KB

-

MFrey ROM MCS-51.svg 325 × 275; 15 KB

-

Microcontroleur detection obstacles.jpg 918 × 611; 89 KB

-

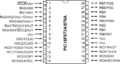

Microcontroller 16F628A.PNG 1,307 × 781; 69 KB

-

Microcontroller 8051.gif 750 × 323; 49 KB

-

MMX registers.png 693 × 1,024; 29 KB

-

MMX-FPU-Register.JPG 457 × 352; 25 KB

-

MMX-Instructions-Overview.jpg 426 × 506; 46 KB

-

Mos 6508.png 215 × 370; 312 KB

-

Mos 7501.png 215 × 370; 14 KB

-

MOS6502.svg 306 × 527; 24 KB

-

MOS8502.svg 306 × 527; 9 KB

-

Motorola 6800.png 215 × 370; 312 KB

-

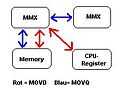

MOV-Instruction.jpg 226 × 169; 9 KB

-

National Semiconductor INS8900 CPU pinout.svg 815 × 760; 7 KB

-

National Semiconductor PACE CPU pinout.svg 815 × 760; 7 KB

-

Niagare.png 1,787 × 1,162; 130 KB

-

Onba04.JPG 253 × 91; 8 KB

-

P6 func diag.png 768 × 1,024; 22 KB

-

PackedData-2.JPG 568 × 367; 26 KB

-

Paraqitja e mënyrës së punës se porteve 1 dhe 3.png 686 × 656; 78 KB

-

PIC arquitecturadibujo.svg 1,164 × 898; 130 KB

-

PIC16F84 brochage.png 622 × 359; 21 KB

-

PIC16F84 minimum.jpg 580 × 239; 26 KB

-

Pic16F876.png 1,176 × 627; 80 KB

-

Piedinatura del MOS 6507.jpg 180 × 224; 12 KB

-

Pinagem8031.jpg 464 × 480; 122 KB

-

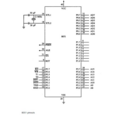

Pinout PIC18F4550.png 573 × 347; 11 KB

-

Playstation 2 architecture.png 1,269 × 786; 54 KB

-

PMADDWD.JPG 542 × 148; 16 KB

-

Port8051.png 449 × 328; 3 KB

-

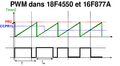

PWMChrono.png 436 × 239; 14 KB

-

PWMdansPIC.png 604 × 734; 72 KB

-

R200 block diagram.svg 1,835 × 1,285; 189 KB

-

Radeon R300 block diagram.svg 720 × 540; 20 KB

-

RCA CDP1802 COSMAC processor pinout.png 1,526 × 1,631; 232 KB

-

RCA COSMAC CDP1802 Microprocessor with Pin Notations.png 220 × 620; 77 KB

-

Register 8086.PNG 426 × 272; 7 KB

-

Rejestr flag 8086.JPG 683 × 252; 25 KB

-

Sbp0400-pin.png 446 × 768; 56 KB

-

Schema de base PIC16F84.jpg 189 × 78; 16 KB

-

Schema jadra 8031.png 670 × 422; 11 KB

-

Schema Kidule 2550 Pinguino.png 929 × 806; 90 KB

-

Schema Kidule Pic 2550 et Ascenseur et De.png 1,000 × 379; 54 KB

-

Schema Kidule Pic 2550 et Ascenseur.png 2,000 × 806; 95 KB

-

Schema PIC16F84 avec Reset enJPG.jpg 669 × 212; 22 KB

-

Schema PIC16F84 avec Reset.jpg 408 × 130; 32 KB

-

Schemat blokowy mikroprocesora 8086.jpg 778 × 581; 59 KB

-

SegmentSelector.svg 288 × 54; 5 KB

-

Silverthorne Schéma Die (Intel Atom).svg 1,024 × 422; 17 KB

-

SpursEngine schema.png 847 × 637; 75 KB

-

SSE registers.svg 150 × 240; 12 KB

-

Texas Instruments TMS1000 processor pinout.png 802 × 1,150; 96 KB

-

The State of Linux Graphics architecture.gif 425 × 322; 31 KB

-

TheveninPort.png 432 × 167; 14 KB

-

Time0 16F84 Inter.png 394 × 254; 17 KB

-

Timer0 18F4550 2.png 515 × 368; 35 KB

-

Timer0 18F4550.png 542 × 255; 27 KB

-

Timer0SLC1657.png 520 × 379; 37 KB

-

Timer1PIC.png 518 × 369; 40 KB

-

Timer2PIC.png 466 × 365; 35 KB

-

Topology CAN protocol.png 669 × 514; 21 KB

-

Transferencia cuádruple.png 790 × 295; 8 KB

-

UltraSPARC3.jpg 1,489 × 884; 314 KB

-

UltraSPARCT1 Die Micrograph DavidHalko.PNG 575 × 610; 23 KB

-

UltraSPARCT2 Die Micrograph DavidHalko.PNG 655 × 550; 25 KB

-

UltraSPARCT3 Die Micrograph DavidHalko.png 508 × 532; 19 KB

-

User Registermodell 68000-page-001.jpg 3,508 × 2,479; 502 KB

-

Wyprowadzenie mikroprocesora 8086.JPG 319 × 509; 31 KB

-

Z180-diagramm-1.jpg 479 × 354; 16 KB

-

Z180-mmu-1.jpg 635 × 426; 21 KB

-

Z80 arch.svg 1,597 × 1,011; 53 KB

-

Z80 pinout.svg 852 × 663; 51 KB

-

Z80-CPU register set.png 543 × 501; 12 KB

-

Zilog z80 daisychain.png 524 × 368; 20 KB

-

Zilog z80 interruptvektor.png 494 × 283; 10 KB

-

Zilog Z80 patent US4332008.pdf 1,158 × 1,702, 29 pages; 1.29 MB

-

Zilog Z80 patent US4486827.pdf 1,158 × 1,702, 23 pages; 1.35 MB

-

Архитектура КР580ИК80.jpg 553 × 495; 50 KB

-

Гарвардская архитектура компьютера.svg 1,512 × 962; 11 KB

-

Пример включения схемы ускоренного переноса в МПС К1804.png 1,217 × 750; 55 KB

-

Система переривань MCS-51.png 656 × 486; 31 KB

-

Структурная схема блока АЛУ К1804ВС2.png 644 × 888; 33 KB

-

Схема архитектуры фон Неймана.svg 510 × 295; 16 KB

-

Схема ускоренного переноса К1804ВР1.png 740 × 1,402; 56 KB

-

Функциональная схема МПС К1804ВС1.png 1,135 × 1,352; 25 KB

-

Функциональная схема МПС К1804ВС2.png 719 × 1,013; 44 KB